2025年6月、半導体の国際会議「VLSI Symposium 2025」で、主要ファウンドリ各社が2nm世代CMOS技術に関する研究成果を発表した。そこで注目されたのは、高集積化を実現できる3次元構造のトランジスタFinFETの限界を超える次世代のトランジスタ技術とされる「Gate-All-Around(GAA)」構造の本格採用だった。

本稿では、GAAについてTSMC、Samsung、Intel、imecの動向を中心に、GAAがどのような変革をもたらすのか、そして本格導入に向けてどのような課題があるのかなどを考察する。

時代はGAAへ。半導体各社の戦略比較

1.FinFETからGAAへ:2nm以降の標準に

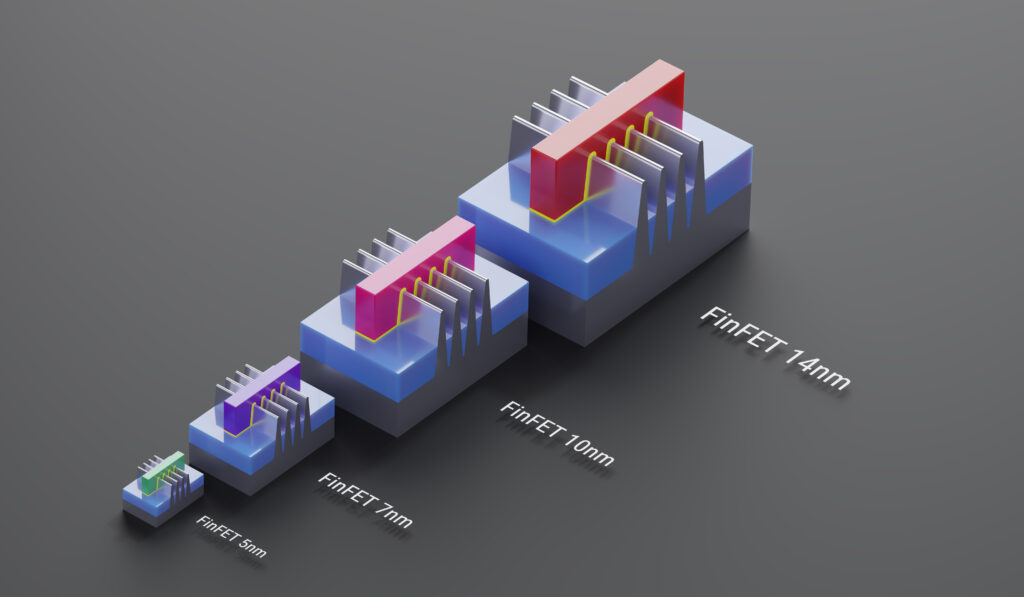

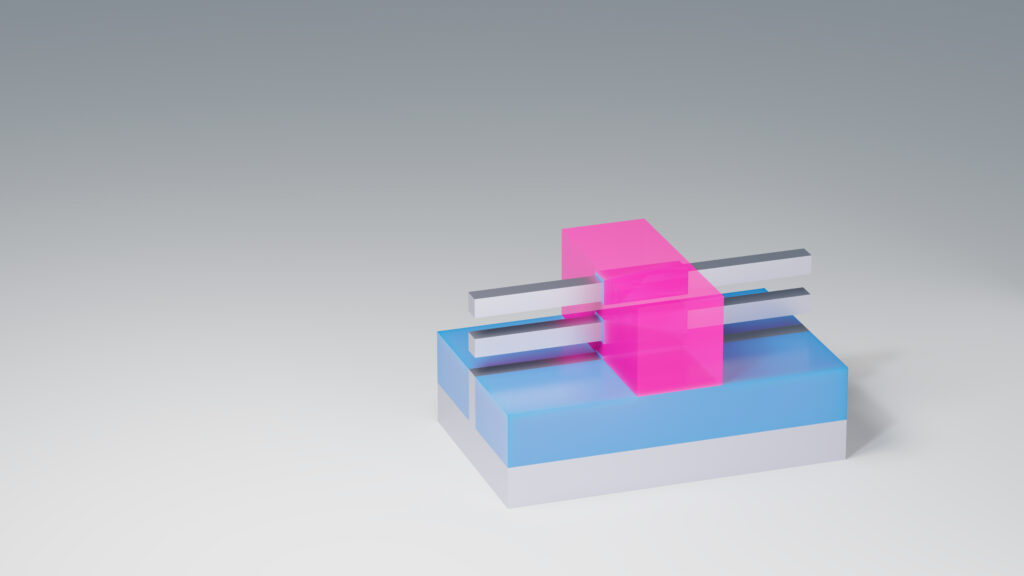

まずはGAAについて、全体の状況から見ていく。前述したようにGAA構造は、3次元構造のトランジスタFinFETの限界を超える次世代のトランジスタ技術と目されている。FinFETは3方向からチャネルを囲んで制御するが、GAAではチャネル全体をゲートで包むことで、リーク電流の低減・性能向上・微細化限界の克服を可能にする。ナノシートやナノワイヤを用いるこの構造は、2nm以降の標準となりつつある。

2. TSMC:顧客ニーズに応じて調整可能なGAAを開発

TSMCは、「N2」プロセスとしてナノシート幅を顧客ニーズに応じて調整可能なGAA技術を開発している。この技術は、トランジスタ密度220 MTr/mm²で、ナノシート幅調整、16層配線という特徴を持つ。2025年下期の量産開始予定で、AMDの次世代EPYC「Venice」チップに適用される予定である。

3. Samsung:PPA改善に特化したAI最適品

Samsungは、2nm「SF2」プロセスをPreferred Networksと共同開発。GAAと2.5Dパッケージを組み合わせ、AI向けチップの性能・消費電力・面積効率(PPA)を改善した。その結果、トランジスタ密度200 MTr/mm²で、低電圧動作、AI最適化を実現した。量産はTSMCより早い2025年中の予定。

4. Intel:PowerVia搭載、EUV対応でTSMC、Samsung圧倒を狙う

Intelは、同社のGAA技術を「RibbonFET」と命名し、裏面電源配線技術「PowerVia」と組み合わせることで、性能25%向上または消費電力36%削減を実現したと発表した。トランジスタ密度は、240 MTr/mm²、PowerVia搭載、EUV対応が特徴。商業化は2026年と前述の2社に比べやや遅れるが、性能面では2社を圧倒できると自信を持つ。

5. imec:トランジスタを縦積みする3D構造を発表

ベルギーのルーベンに拠点を置く研究機関imecは、サブ2nm以降のGAA拡張構造「Outer Wall Forksheet(OWF)」を発表した。トランジスタを縦積みする3D構造や、高性能材料との融合などで、トランジスタ密度230 MTr/mm²を実現している。

実用化のハードル高いGAA。日本にとっては大きなチャンスか

このようにGAA構造は非常に有望な技術と言える。しかし、本格実用化に向けた課題も多いのも事実。たとえば、ナノシートの寸法ばらつき制御、EUV露光時の損傷対策など、ハードルは高い。

とはいえ、日本の装置・材料メーカーからすると、今後の出方次第ではある意味チャンスとも言える。成膜(ALD/CVD)、リソグラフィ周辺材料、寸法検査技術など、GAA実装を支える要素技術は日本の得意分野だからだ。2nm世代CMOS技術は単なる微細化だけの勝負ではなく、製造プロセス総合力の勝負に変わりつつあるのだ。

参考リンク一覧

(参考:VLSI Symposium 2025 プログラム(2025年6月))

(参考:AMD、TSMC N2による「Venice」チップのテープアウト)

(参考:TSMC、N2プロセスの欠陥密度に関する技術説明)

(参考:Samsung、2nm GAAおよび2.5Dパッケージ対応チップ発表(2025年6月))

(参考:Intel、RibbonFETとPowerViaの詳細発表(2025年VLSI))

(参考:imec、Forksheet技術をVLSI 2025で発表)

-

求人

デバイス開発エンジニア この分野に関連する最新の求人情報はこちら›

-

求人

前工程プロセス開発 この分野に関連する最新の求人情報はこちら›

-

求人

プロセス技術研究者 この分野に関連する最新の求人情報はこちら›