これまでの半導体業界は、パッケージ設計・回路設計・材料開発といったそれぞれの専門ごとの“垂直分業”によって支えられてきたと言ってよいだろう。しかし近年、CoWoS(Chip on Wafer onSubstrate)や FOWLP(Fan-Out Wafer-Level Packaging)、SoIC(System on Integrated Chips)といった 3D 実装技術の進化により、その分業体制にひずみが生じている。

TSMC が 2023 年の「Open Innovation Platform Symposium」で強調したのは、SoIC における“統合設計”の重要性だった。チップ間通信の最適化には、電気特性だけでなく熱伝導や材料特性を含む横断的な視点が不可欠であり、もはや単一分野の知識では対応できないからだ。

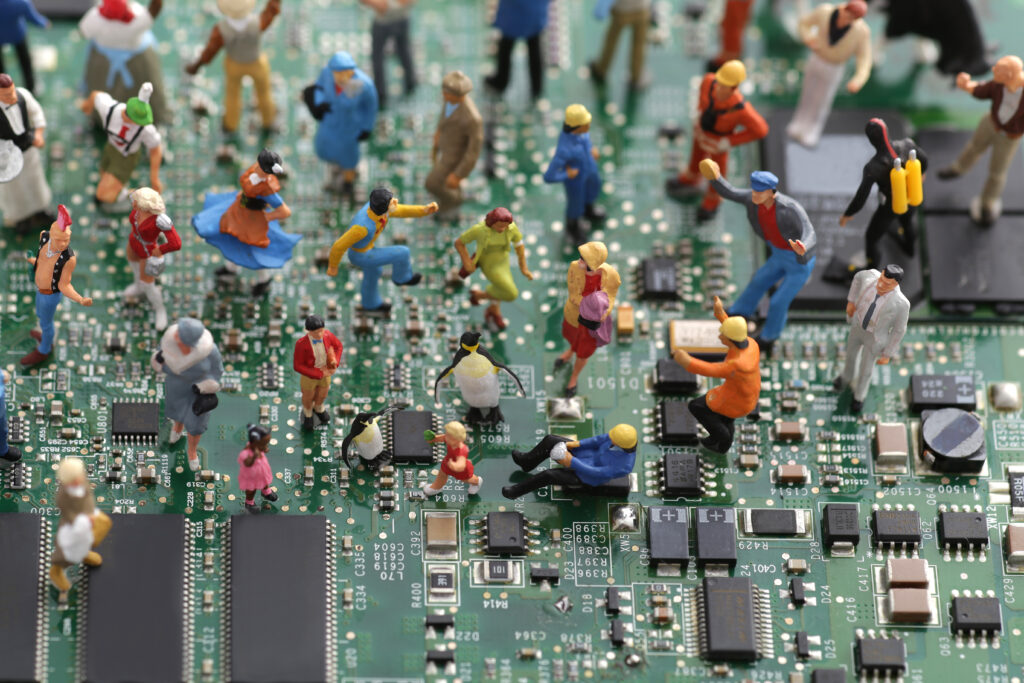

この変化に対応できるのは、それぞれの領域における「深い専門性」と「他領域との横断的な知識」を兼ね備えた人材だけだ。今、OSAT やファウンドリ、材料メーカーの現場で求められているのは、このような「つなぐ力」を持つ技術者である。本稿では、このような“垂直分業”の終焉と今後必要となる “橋渡し役”なスキルを持つ人材について考察する。

なぜ今、「領域横断スキル」が必須なのか

1.先端パッケージの進化がもたらした「橋渡しの必要性」

先端パッケージでは、配線密度、熱伝導率、材料の Cte(熱膨張係数)など、複数領域のパラメータが密接に連動している。たとえば、NVIDIA の「H100」に採用された CoWoS 技術では、HBM とGPU ダイを重ねて高帯域を実現するが、そこでは高精度な再配線(RDL)設計と高度な熱マネジメントが同時に必要となる。

これらはもはや個別の部門だけでは最適化できず、設計・解析・材料・製造プロセスを横断する知識がなければ成立しない。

2.電気・熱・材料をつなぐ「ハイブリッド人材」

今、現場で必要とされているのは、「再配線層の設計ができて、熱シミュレーションも読めて、材料の応力も理解している」といった、幅広い知識と経験を持ち、多様な状況に対応できる人材なのだ。

特に FOWLP では、チップ外周へのファンアウトや、樹脂と配線の界面剥離といった複雑な課題があり、設計者が材料物性を理解しているかどうかが致命的差異を生む。このため、幅広い知識と経験を持ち、多様な状況に対応できる人材、つまり「ハイブリット人材」が不可欠になる。

3.産学連携が加速する教育現場──各国の再教育モデルとは

海外では、こうした変化に対応するための技術者育成が加速している。たとえば、台湾・NARLabs と国立清華大学は、TSMC や ASEと連携し、熱・電気・材料の連携設計を学べる産学講座を整備。実務者向けの夜間講座も提供している(出典:NARLabs)。

一方、アメリカでは IMAPS(国際マイクロエレクトロニクス会議)がオンラインで実装技術の講座を展開。さらに、Cadence やANSYS といった EDA 企業も、先端パッケージ向けの専用カリキュラムを拡充している。

分断されていた領域をつなぐ「知の融合」が次世代の成長を担う

先端パッケージがもたらす複雑性は、単なる設計手法の変化だけではない。そこには、かつて分断されていた領域をつなぐ「知の融合」が必要とされている。だからこそ、「分業の谷間」に橋をかけることのできる人材が、次の開発プロジェクトを動かす鍵を握る。

経済産業省が掲げる「半導体・デジタル産業戦略」でも、大学・高専・企業が連携して実践教育を進める方針が示されており、技術者再教育が国家戦略としても位置付けられ始めている。

(出典:経済産業省)

-

求人

材料開発エンジニア この分野に関連する最新の求人情報はこちら›

-

求人

後工程プロセス開発 この分野に関連する最新の求人情報はこちら›

-

求人

設計エンジニア この分野に関連する最新の求人情報はこちら›